Program overview:

This solution is based on the main control platform CVITEK_CV1821 and sensor SOI_Q03P, and is used in intelligent surveillance IP cameras, which can be used outdoors or indoors. It uses a resolution of 2304x1296, a frame rate of 30, and supports HDR. As a 3M surveillance camera, it uses ISP image adjustment technology to improve imaging quality and color reality, and uses a dedicated CMOS sensor and post-processing to achieve stronger photosensitivity and less noise.

Product overview:

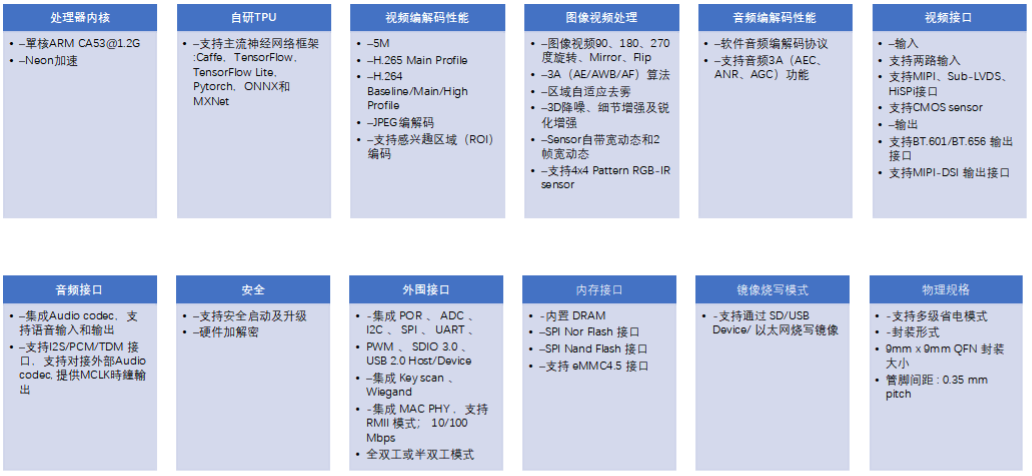

1. Main control:

CVITEK is an open artificial intelligence chip developer, focusing on the research and development of video surveillance and edge computing technology. It has the best-performing AI TPU computing core and SOC chip integration technology in the country. Its current research and development fields cover SOC chip design, AI TPU processor and tool chain, image processing algorithms and design, etc. It is committed to creating a one-stop platform solution for artificial intelligence machine vision, bringing customers rich value and technologically innovative products and services. CV1821 is a high-performance, low-power chip launched for edge intelligent surveillance IP cameras, local face recognition attendance machines, smart homes and other product fields. It integrates the H.264/H.265 video compression codec and ISP; it supports HDR wide dynamic range, 3D noise reduction, defogging, lens distortion correction and other image enhancement and correction algorithms to provide customers with professional-level video image quality.

The chip also integrates a self-developed TPU that can provide about 0.5TOPS computing power under INT8 computing. The specially designed TPU scheduling engine can effectively provide extremely high bandwidth data flow for the tensor processor core; and provides users with a powerful deep learning model compiler and Linux software SDK development package. Mainstream deep learning frameworks, such as Caffe Pytorch ONNX MXNet and TensorFlow (Lite) framework mainstream networks can be easily transplanted to the platform.

Main features

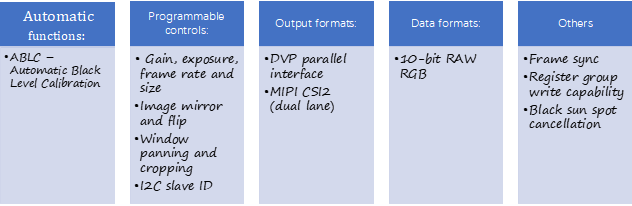

2.Sensor

Crystal Phase Optoelectronics (SOI) is a company focused on the development and sales of CMOS image sensors (CIS). The company has an excellent design team and cooperates with professional wafer fabs, with system integration capabilities and cooperative relationships with test and packaging manufacturers. Crystal Phase Optoelectronics has launched low-cost, high-performance and diversified products to meet the needs of the market and customers, and provides fast local customer service to make customers competitive in production efficiency and time.

JX-Q03P is a high-performance 3.0MP BSI CMOS image sensor designed and manufactured using SOI's 2.0um pixel technology. The JX-Q03P consists of a 2304x 1296 active pixel sensor (APS) array with on-chip 10-bit ADC, programmable gain control (PGA) and correlated double sampling (CDS) functions to significantly reduce fixed pattern noise (FPN). The sensor also has many standard programmable and automatic features. It supports both industry-standard DVP parallel interface and MIPI CSI2 dual data lane serial interface. External host controllers can access the device through a standard serial interface. The sensor is available as a wafer-level packaged CSP.

Main features

Effect display

The following are renderings taken in different environments:

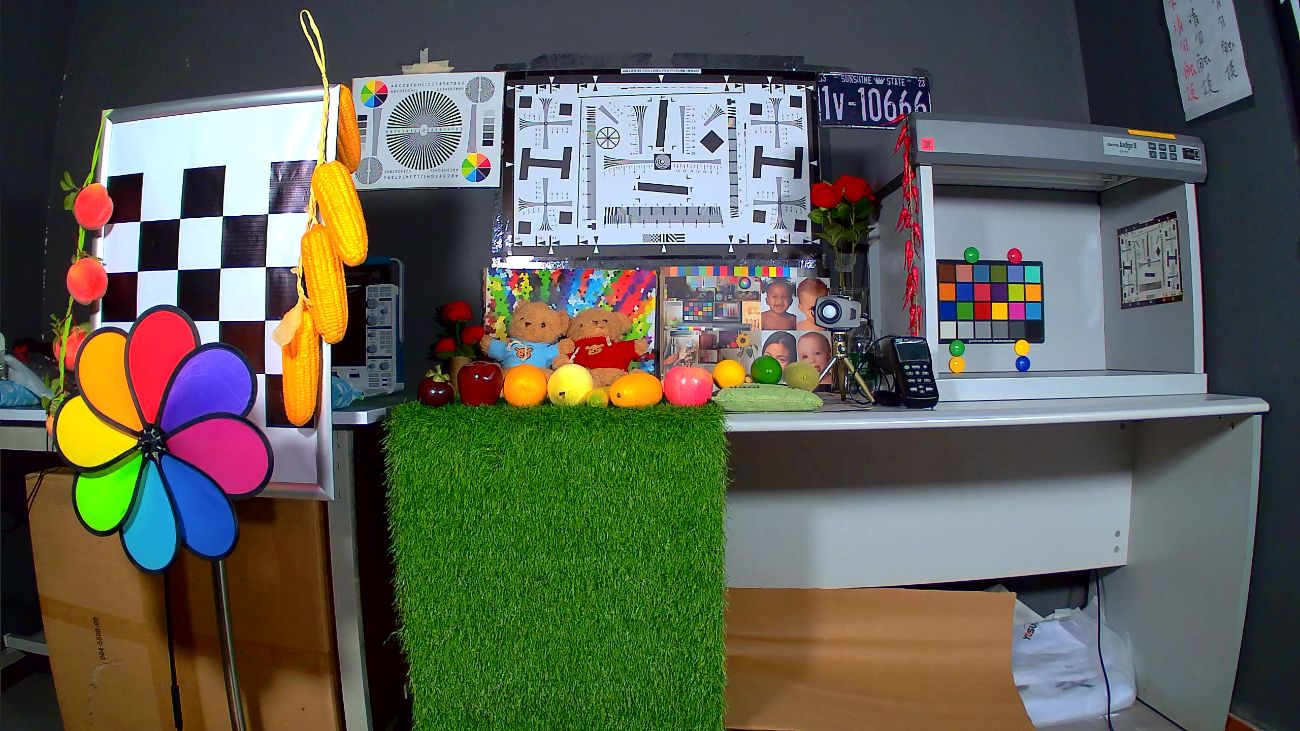

100lux:

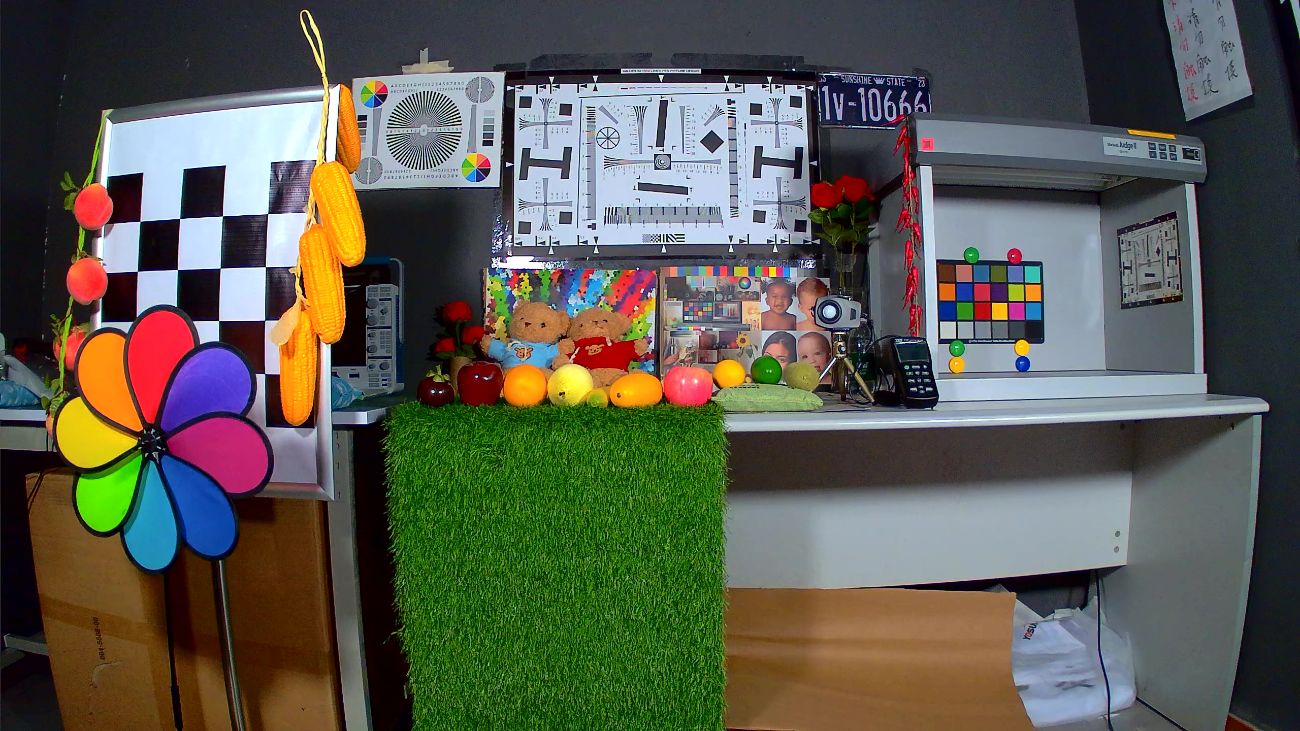

50lux:

30lux:

10lux:

1lux:

0 lux:

Infrared 850nm:

Infrared 940nm:

►Scenario application diagram

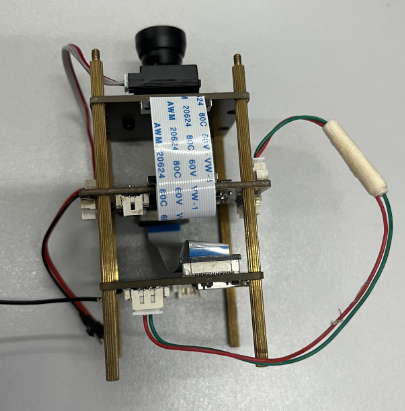

►Display board photo

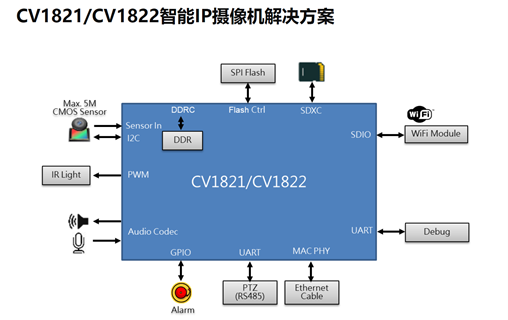

►Solution block diagram

►Core technology advantages

1. CV1821 is a high-performance, low-power chip launched for edge intelligent surveillance IP cameras, local face recognition attendance machines, smart homes and other product fields. It integrates the H.264/H.265 video compression codec and ISP;

2. Supports HDR wide dynamic range, 3D noise reduction, defogging, lens distortion correction and other image enhancement and correction algorithms to provide customers with professional-level video image quality; 3. The chip is more integrated with the self-developed TPU, which can provide about 0.5TOPS computing power under INT8 operation;

4. The specially designed TPU scheduling engine can effectively provide extremely high bandwidth data flow for the tensor processor core;

5. It also provides users with a powerful deep learning model compiler and Linux software SDK development kit;

6. Mainstream deep learning frameworks, such as Caffe, Pytorch, ONNX MXNet and the mainstream networks of TensorFlow (Lite) framework, can be easily transplanted to the platform.

►Project specifications

1. Main control cv1821 specifications: .Single-core ARM [email protected]; .Image and video 90, 180, 270 degree rotation, Mirror, Flip; .MiPi interface; .9mm x 9mm QFN package size; .Integrated POR, ADC, I2C, SPI, UART, PWM, SDIO 3.0, USB 2.0 Host/Device; .Built-in DRAM; 2. sensor_soi_Q03P specifications: 3.0MP CMOS image sensor; 3. Resolution: 2304*1296; .10-bit RAW RGB; .DVP parallel and MIPI CSI2 dual data channel serial interface;